## **SANYO Semiconductors**

# DATA SHEET

An ON Semiconductor Company

**Bi-CMOS LSI**

# LV5744V — 2-channel Step-down Switching Regulator

#### Overview

The LV5744V is a 2-channel step-down switching regulator.

#### **Features**

- Provides dual switching regulator control circuits integrated on the chip.

- Output-stage push-pull structure enabling high efficient operation.

- Provides power supply (V<sub>CC</sub>-5V) for protecting the external P channel MOS gate.

- Built-in timer latch type SCP (short-circuit protection circuit)

- Built-in UVLO (Low voltage malfunction prevention circuit)

- Built-in reference voltage circuit

- Max\_On\_Duty is adjustable.

#### **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   |                                                                 | Symbol              | Conditions                     | Ratings     | Unit |

|-----------------------------|-----------------------------------------------------------------|---------------------|--------------------------------|-------------|------|

| Maximum supply voltage      |                                                                 | V <sub>CC</sub> max |                                | 35          | V    |

| Output voltage              |                                                                 | V <sub>O</sub> max  |                                | 33          | V    |

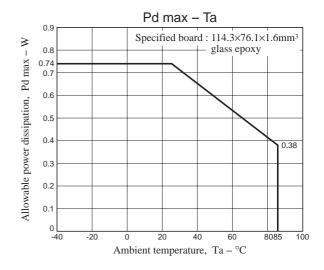

| Allowable power dissipation |                                                                 | Pd max              | Mounted on a specified board * | 0.74        | W    |

| Operating temperature       |                                                                 | Topr                |                                | -40 to +85  | °C   |

| Storage temperature         |                                                                 | Tstg                |                                | -55 to +150 | °C   |

| Allowa                      | Allowable pin voltage                                           |                     |                                |             |      |

| 1                           | CT, NON1, NON2,<br>INV1, INV2, FB1, FB2,<br>DT1, DT2, SCP, VREF |                     |                                | 7           | V    |

| 2                           | V <sub>CC</sub> -5V                                             |                     |                                | 30          | V    |

| 3                           | GND, OUT1, OUT2,                                                |                     |                                | 35          | V    |

<sup>\*:</sup> Specified board: 114.3×76.1×1.6mm³, glass epoxy board

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

# LV5744V

# Allowable Operating Ratings at Ta = 25°C

| Parameter                     | Symbol          | Conditions | Ratings    | Unit |

|-------------------------------|-----------------|------------|------------|------|

| Supply voltage                | Vcc             |            | 8 to 33    | V    |

| Error amplifier input voltage | VIN             |            | 0 to 3.3   | V    |

| Timing capacitance            | C <sub>CT</sub> |            | 50 to 5000 | pF   |

| Oscillation frequency         | FCT             |            | 20k to 1M  | Hz   |

## **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 12V$

| Dorometer                           | Cumhal           | O a a Pirita a a           |                      | Ratings              |                      |      |

|-------------------------------------|------------------|----------------------------|----------------------|----------------------|----------------------|------|

| Parameter                           | Symbol           | Conditions                 | min                  | typ                  | max                  | Unit |

| Reference voltage block             |                  |                            |                      |                      |                      |      |

| Output voltage                      | Vref             | Iref = 1mA                 | 2.4948               | 2.520                | 2.5452               | V    |

| Input stability                     | V <sub>DLI</sub> | V <sub>CC</sub> = 8 to 33V |                      | 1                    | 10                   | mV   |

| Load stability                      | V <sub>DLO</sub> | Iref = 0 to 5mA            |                      | 1                    | 10                   | mV   |

| V <sub>IN</sub> -5V supply voltage  | V <sub>N5</sub>  | I <sub>OUT</sub> = -5mA    | V <sub>CC</sub> -5.5 | V <sub>CC</sub> -5.0 | V <sub>CC</sub> -4.5 | V    |

| Triangular wave oscillator block    |                  |                            |                      |                      |                      |      |

| Oscillation frequency               | Fosc             | C <sub>CT</sub> = 220pF    | 320                  | 400                  | 480                  | kHz  |

| Frequency fluctuation               | F <sub>DV</sub>  | V <sub>CC</sub> = 8 to 33V |                      | 1                    |                      | %    |

| Protection circuit block            |                  |                            |                      |                      |                      |      |

| Threshold voltage                   | VIT              |                            | 1.5                  | 1.7                  | 1.9                  | V    |

| Standby voltage                     | V <sub>STB</sub> |                            |                      | 50                   | 100                  | mV   |

| Latch voltage                       | V <sub>LT</sub>  |                            |                      | 30                   | 100                  | mV   |

| Source current                      | ISCP             |                            | 1.6                  | 2.1                  | 2.6                  | μА   |

| Comparator threshold voltage        | VCT              |                            | 1.4                  | 1.5                  | 1.6                  | V    |

| Quiescent time adjustment circuit l | block            |                            |                      |                      |                      |      |

| Input threshold voltage             | Vt0              | Duty cycle = 0%            | 0.45                 | 0.5                  | 0.55                 | V    |

| (fosc = 20kHz)                      | Vt100            | Duty cycle = 100%          | 0.95                 | 1.0                  | 1.05                 | ٧    |

| Input bias current                  | I <sub>BDT</sub> | DT1, DT2 = 0V              |                      | 0.1                  | 1                    | μΑ   |

| Low voltage malfunction prevention  | n circuit block  |                            |                      |                      |                      |      |

| Threshold voltage                   | V <sub>UT</sub>  |                            | 6.5                  | 7                    | 7.5                  | >    |

| Error amplifier                     |                  |                            |                      |                      |                      |      |

| Input offset voltage                | V <sub>IO</sub>  |                            |                      |                      | 6                    | mV   |

| Input offset current                | IIO              |                            |                      |                      | 30                   | nA   |

| Input bias current                  | I <sub>IB</sub>  |                            |                      | 15                   | 100                  | nA   |

| Open gain                           | AV               |                            |                      | 85                   |                      | dB   |

| Common mode input voltage range     | V <sub>OM</sub>  | V <sub>CC</sub> = 8 to 33V | 0                    |                      | 3.3                  | V    |

| Common mode rejection ratio         | CMRR             |                            |                      | 80                   |                      | dB   |

| Maximum output voltage              | VOH              |                            |                      | 2.6                  |                      | V    |

| Minimum output voltage              | V <sub>OL</sub>  |                            |                      | 0.2                  | 0.4                  | V    |

| Output sink current                 | loi              | FB = 1.25V                 |                      | 1                    |                      | mA   |

| Output source current               | 100              | FB = 1.25V                 |                      | 85                   |                      | μА   |

| PWM comparator                      |                  |                            |                      |                      |                      |      |

| Input threshold voltage             | Vt0              | Duty cycle = 0%            | 0.45                 | 0.5                  | 0.55                 | V    |

| (fosc = 20kHz)                      | Vt100            | Duty cycle = 100%          | 0.95                 | 1.0                  | 1.05                 | V    |

| Output block                        |                  |                            |                      |                      |                      |      |

| Output stage on resistance (upper)  | RONH             |                            |                      | 7                    |                      | Ω    |

| Output stage on resistance (lower)  | R <sub>ONL</sub> |                            |                      | 2                    |                      | Ω    |

| Overall device characteristics      |                  |                            |                      |                      |                      |      |

| Standby current                     | Iccs             | When output is off         |                      |                      | 10                   | mA   |

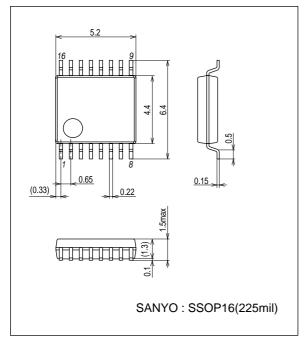

# **Package Dimensions**

unit: mm (typ)

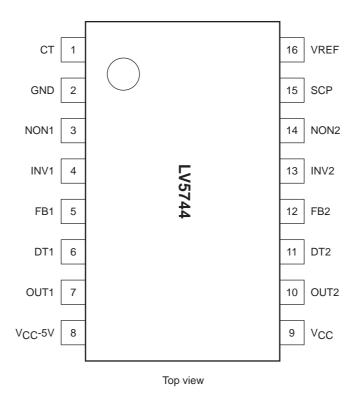

# **Pin Assignment**

### **Pin Function**

| Pin No. | Pin Name            | Description                              |  |

|---------|---------------------|------------------------------------------|--|

| 1       | СТ                  | External timing capacitor connection pin |  |

| 2       | GND                 | Ground                                   |  |

| 3       | NON1                | Error amplifier 1 input (+)              |  |

| 4       | INV1                | Error amplifier 1 input (-)              |  |

| 5       | FB1                 | Error amplifier 1 output                 |  |

| 6       | DT1                 | Output 1 maximum duty setting            |  |

| 7       | OUT1                | Output 1                                 |  |

| 8       | V <sub>CC</sub> -5V | Power supply for output stage drive      |  |

| 9       | V <sub>CC</sub>     | Power supply                             |  |

| 10      | OUT2                | Output 2                                 |  |

| 11      | DT2                 | Output 2 maximum duty setting            |  |

| 12      | FB2                 | Error amplifier 2 input (+)              |  |

| 13      | INV2                | Error amplifier 2 input (-)              |  |

| 14      | NON2                | Error amplifier 2 output                 |  |

| 15      | SCP                 | Timer latch setting                      |  |

| 16      | VREF                | Reference voltage output                 |  |

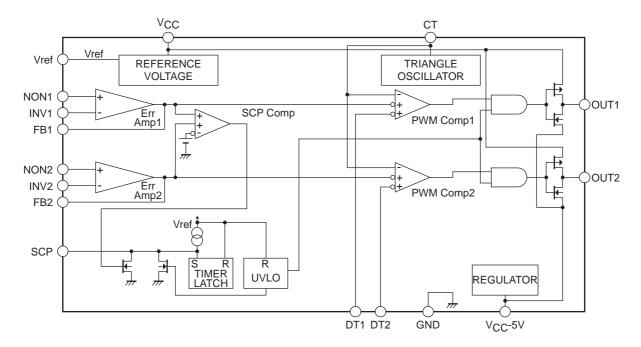

## **Block Diagram**

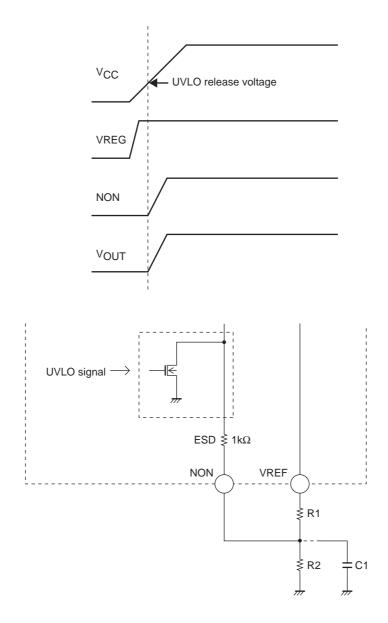

### **Timing Chart**

<sup>\*</sup> The voltage at the NON pin is  $\{VREF/(R1+1k)\} \times 1k$  in UVLO mode.

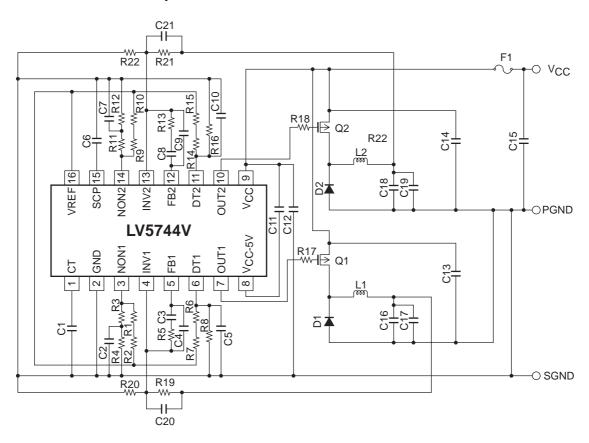

#### **Application Circuit Example**

- Specifications of any and all SANYO Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Semiconductor Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Semiconductor Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of June, 2008. Specifications and information herein are subject to change without notice.