# ARM<sup>®</sup> DSTREAM<sup>®</sup> and RVI<sup>®</sup>

Using the Debug Hardware Configuration Utilities

Copyright © 2010 ARM. All rights reserved. ARM DUI 0498B (ID121610)

### **ARM DSTREAM and RVI** Using the Debug Hardware Configuration Utilities

Copyright © 2010 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

|               |       |                  |                | Change history |

|---------------|-------|------------------|----------------|----------------|

| Date          | Issue | Confidentiality  | Change         |                |

| May 2010      | А     | Non-Confidential | First release. |                |

| November 2010 | В     | Non-Confidential | Second Release |                |

#### **Proprietary Notice**

Words and logos marked with \* or \* are registered trademarks or trademarks of ARM\* in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

This product includes software developed by the Apache Software Foundation (see http://www.apache.org).

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

Change bistom

#### **Conformance Notices**

This section contains conformance notices.

#### Federal Communications Commission Notice

This device is test equipment and consequently is exempt from part 15 of the FCC Rules under section 15.103 (c).

#### Class A

Important: This is a Class A device. In residential areas, this device may cause radio interference. The user should take the necessary precautions, if appropriate.

CE Declaration of Conformity

## Cť

The system should be powered down when not in use.

It is recommended that ESD precautions be taken when handling DSTREAM, RVI, and RVT equipment.

The DSTREAM, RVI, and RVT modules generate, use, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- ensure attached cables do not lie across the target board

- reorient the receiving antenna

- increase the distance between the equipment and the receiver

- connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- consult the dealer or an experienced radio/TV technician for help

— Note —

It is recommended that wherever possible shielded interface cables be used.

## Contents ARM DSTREAM and RVI Using the Debug Hardware Configuration Utilities

| Chapter 1 | Con  | ventions and feedback                                       |      |

|-----------|------|-------------------------------------------------------------|------|

| Chapter 2 | Gett | ing started with the debug hardware configuration utilities |      |

| -         | 2.1  | About the debug hardware configuration utilities            | 2-2  |

|           | 2.2  | Starting the debug hardware configuration utilities         | 2-3  |

|           | 2.3  | Scanning for available debug hardware units                 |      |

|           | 2.4  | Identifying a debug hardware unit                           | 2-7  |

|           | 2.5  | Connecting to a debug hardware unit                         |      |

| Chapter 3 | Con  | figuring network settings for your debug hardware unit      |      |

| -         | 3.1  | About configuring network settings                          | 3-2  |

|           | 3.2  | Determining the correct network settings                    | 3-3  |

|           | 3.3  | The Configure debug_hardware device dialog box              | 3-4  |

|           | 3.4  | The Configure new debug_hardware device dialog box          | 3-6  |

|           | 3.5  | Debug hardware unit network settings                        |      |

|           | 3.6  | Configuring the network settings for a debug hardware unit  | 3-8  |

|           | 3.7  | Modifying the network settings for a debug hardware unit    | 3-10 |

|           | 3.8  | Restarting your debug hardware unit                         |      |

|           | 3.9  | Troubleshooting                                             | 3-13 |

| Chapter 4 | Man  | aging the firmware on your debug hardware unit              |      |

| -         | 4.1  | About templates                                             | 4-2  |

|           | 4.2  | Viewing software version numbers                            | 4-3  |

|           | 4.3  | Installing a firmware update or patch                       | 4-4  |

|           | 4.4  | Upgrading an LVDS probe                                     |      |

|           | 4.5  | Restarting the debug hardware unit in RVI Update            |      |

| Chapter 5 | Creat | Creating debug hardware target configurations                                              |        |  |  |  |  |  |

|-----------|-------|--------------------------------------------------------------------------------------------|--------|--|--|--|--|--|

|           | 5.1   | About creating debug hardware target configurations                                        | 5-3    |  |  |  |  |  |

|           | 5.2   | Creating a debug hardware configuration file                                               |        |  |  |  |  |  |

|           | 5.3   | Opening an existing debug hardware configuration file in RVConfig                          | 5-6    |  |  |  |  |  |

|           | 5.4   | Configuring a JTAG scan chain                                                              |        |  |  |  |  |  |

|           | 5.5   | About configuring a device list                                                            |        |  |  |  |  |  |

|           | 5.6   | Autoconfiguring a scan chain                                                               | . 5-11 |  |  |  |  |  |

|           | 5.7   | Adding devices to the scan chain                                                           |        |  |  |  |  |  |

|           | 5.8   | Removing devices from the scan chain                                                       |        |  |  |  |  |  |

|           | 5.9   | Changing the order of devices on the scan chain                                            |        |  |  |  |  |  |

|           | 5.10  | Select Platform dialog box                                                                 |        |  |  |  |  |  |

|           | 5.11  | Export As Platform dialog box                                                              |        |  |  |  |  |  |

|           | 5.12  | Exporting a configuration to a platform file                                               |        |  |  |  |  |  |

|           | 5.13  | Device Properties dialog box                                                               |        |  |  |  |  |  |

|           | 5.14  | Changing the properties of a device                                                        |        |  |  |  |  |  |

|           | 5.15  | Setting the clock speed                                                                    |        |  |  |  |  |  |

|           | 5.16  | About adaptive clocking                                                                    |        |  |  |  |  |  |

|           | 5.17  | Device configuration settings                                                              |        |  |  |  |  |  |

|           | 5.18  | Debug hardware Advanced settings                                                           | 5-33   |  |  |  |  |  |

|           | 5.19  | Trace configuration settings                                                               |        |  |  |  |  |  |

|           | 5.20  | Configuring Reset options in debug hardware                                                |        |  |  |  |  |  |

|           | 5.21  | Configuring SecurCore behavior if the processor clock stops when stepping instruct<br>5-38 | ions   |  |  |  |  |  |

|           | 5.22  | Configuring TrustZone enabled processor behavior when debug privileges are reduce 5-39     | ced    |  |  |  |  |  |

|           | 5.23  | About platform detection and selection                                                     | . 5-40 |  |  |  |  |  |

|           | 5.24  | Autodetecting a platform                                                                   | . 5-41 |  |  |  |  |  |

|           | 5.25  | Manually selecting a platform                                                              |        |  |  |  |  |  |

|           | 5.26  | Clearing a platform assignment from a debug hardware configuration                         |        |  |  |  |  |  |

|           | 5.27  | Adding new platforms                                                                       |        |  |  |  |  |  |

|           | 5.28  | Adding autoconfigure support for new platforms                                             |        |  |  |  |  |  |

|           | 5.29  | Configuring the debug hardware Advanced settings                                           |        |  |  |  |  |  |

|           | 5.30  | Saving your changes                                                                        |        |  |  |  |  |  |

|           | 5.31  | Disconnecting from a debug hardware unit                                                   |        |  |  |  |  |  |

|           | 5.32  | Configuring a target processor for virtual Ethernet                                        |        |  |  |  |  |  |

|           | 5.33  | CoreSight device names and classes                                                         |        |  |  |  |  |  |

| Chapter 6 | Conf  | iguring CoreSight systems                                                                  |        |  |  |  |  |  |

|           | 6.1   | About CoreSight system configuration                                                       |        |  |  |  |  |  |

|           | 6.2   | Reading the CoreSight ROM table                                                            |        |  |  |  |  |  |

|           | 6.3   | CoreSight autodetection                                                                    |        |  |  |  |  |  |

|           | 6.4   | Autodetecting Serial Wire Debug                                                            | 6-5    |  |  |  |  |  |

|           | 6.5   | About trace associations                                                                   |        |  |  |  |  |  |

|           | 6.6   | Defining CoreSight trace associations                                                      | 6-7    |  |  |  |  |  |

|           | 6.7   | Format of trace associations                                                               |        |  |  |  |  |  |

|           | 6.8   | Trace Association Editor dialog box                                                        | 6-9    |  |  |  |  |  |

|           | 6.9   | Setting up a CoreSight trace association file                                              | . 6-11 |  |  |  |  |  |

|           | 6.10  | Loading a trace association file                                                           | . 6-13 |  |  |  |  |  |

|           | 6.11  | CoreSight topology and associations for the CoreSight DK11                                 | . 6-15 |  |  |  |  |  |

|           | 6.12  | CoreSight topology and associations for the Cortex-R4 FPGA                                 | . 6-17 |  |  |  |  |  |

|           | 6.13  | CoreSight topology and associations for the Cortex-M3 FPGA                                 | . 6-19 |  |  |  |  |  |

|           | 6.14  | CoreSight topology and associations for multiple trace sources                             | . 6-21 |  |  |  |  |  |

|           | 6.15  | Configuring CoreSight processors                                                           |        |  |  |  |  |  |

|           | 6.16  | Configuring ARM7, ARM9, and ARM11 processors in CoreSight systems                          | 6-23   |  |  |  |  |  |

|           | 6.17  | Configuring CoreSight systems with multiple devices per JTAG-AP multiplexor port           | 6-25   |  |  |  |  |  |

| Chapter 7 |       | g Trace                                                                                    |        |  |  |  |  |  |

|           | 7.1   | About using trace hardware                                                                 |        |  |  |  |  |  |

|           | 7.2   | Trace hardware capture rates                                                               |        |  |  |  |  |  |

|           | 7.3   | Configuring trace lines (DSTREAM and RVT2 only)                                            | /-4    |  |  |  |  |  |

|            | 7.4  | Configuring your debugger for trace capture                                     | 7-6   |

|------------|------|---------------------------------------------------------------------------------|-------|

| Chapter 8  | Debi | ugging with your debug hardware unit                                            |       |

|            | 8.1  | Post-mortem debugging                                                           | 8-2   |

|            | 8.2  | Semihosting                                                                     |       |

|            | 8.3  | Adding an application SVC handler when using debug hardware                     |       |

|            | 8.4  | Cortex-M3 semihosting                                                           |       |

|            | 8.5  | Hardware breakpoints                                                            |       |

|            | 8.6  | Software instruction breakpoints                                                |       |

|            | 8.7  | Processor exceptions                                                            |       |

|            | 8.8  | Breakpoints and the program counter                                             |       |

|            | 8.9  | Interaction between breakpoint handling in the debug hardware and your debugger |       |

|            | 8.10 | Problems setting breakpoints                                                    |       |

|            | 8.11 | Strategies used by debug hardware to debug cached processors                    |       |

|            | 8.12 | Considerations when debugging processors with caches enabled                    |       |

|            | 8.13 | Debugging applications in ROM                                                   |       |

|            | 8.14 | Debugging from reset                                                            | 8-18  |

|            | 8.15 | Debugging with a simulated reset                                                |       |

|            | 8.16 | Debugging with a reset register                                                 | 8-20  |

|            | 8.17 | Debugging with a target reset                                                   | 8-21  |

|            | 8.18 | Debugging systems with ROM at the exception vector                              | 8-22  |

| Chapter 9  | Conf | iguring debug hardware for GDB                                                  |       |

|            | 9.1  | About configuring debug hardware for debugging with GDB                         | 0_3   |

|            | 9.2  | Feature support when debugging with GDB                                         |       |

|            | 9.3  | Debugging modes for GDB                                                         |       |

|            | 9.4  | Debug hardware TCP/IP port numbering                                            |       |

|            | 9.5  | DCC modes                                                                       |       |

|            | 9.6  | Building for standalone target platforms                                        |       |

|            | 9.7  | Methods of connecting from remote GDB sessions                                  |       |

|            | 9.8  | Connection methods for each debugging mode                                      |       |

|            | 9.9  | Connections to a target without built-in GDB support (RVI-GDB)                  |       |

|            | 9.10 | Connections to a target with a GDB stub (Target-GDB)                            | 9-13  |

|            | 9.11 | Connections to a target GDB stub using Virtual Ethernet/TTY mode (Target-GDB-Vi |       |

|            |      | Ethernet)                                                                       | 9-15  |

|            | 9.12 | Connections to a target OS using gdbserver (GDBserver)                          | 9-17  |

|            | 9.13 | Connections to a target OS using NFS (GDB-NFS)                                  | 9-19  |

|            | 9.14 | Preparing your debug hardware for remote GDB connections                        | 9-21  |

|            | 9.15 | Connecting to targets from GDB through debug hardware                           | 9-22  |

|            | 9.16 | Setting DCC parameters                                                          |       |

|            | 9.17 | DCC and interrupts                                                              | 9-25  |

|            | 9.18 | Loading and booting a complete system                                           | 9-26  |

|            | 9.19 | rvigdbconfig command syntax                                                     | 9-27  |

|            | 9.20 | rviload command syntax                                                          | 9-28  |

|            | 9.21 | RVIahbload command syntax                                                       |       |

|            | 9.22 | RVIvec command syntax                                                           |       |

|            | 9.23 | Multiprocessor debugging with GDB and debug hardware                            | 9-34  |

| Chapter 10 | Trou | bleshooting your debug hardware unit                                            |       |

| •          | 10.1 | Multiple programs attempting to scan                                            | 10-2  |

|            | 10.2 | USB server not accessible                                                       |       |

|            | 10.3 | Connection times out                                                            |       |

|            | 10.4 | Other active connections                                                        | 10-5  |

|            | 10.5 | A debug hardware unit is not listed                                             |       |

|            | 10.6 | Auto Configure button is disabled in RVConfig                                   |       |

|            | 10.7 | Remove button is disabled in RVConfig                                           |       |

|            | 10.8 | Troubleshooting firmware upgrade installations                                  |       |

|            | 10.9 | Troubleshooting autoconfigation of a scan chain                                 | 10-11 |

## Chapter 1 Conventions and feedback

The following describes the typographical conventions and how to give feedback:

#### **Typographical conventions**

The following typographical conventions are used:

| monospace Denotes text that can be entered at the keyboard, such as commands, f | ĩle |

|---------------------------------------------------------------------------------|-----|

| and program names, and source code.                                             |     |

monospace Denotes a permitted abbreviation for a command or option. The underlined text can be entered instead of the full command or option name.

#### monospace italic

Denotes arguments to commands and functions where the argument is to be replaced by a specific value.

#### monospace bold

| Denote | s language | keywords | when used | loutside | example code | ;. |

|--------|------------|----------|-----------|----------|--------------|----|

|--------|------------|----------|-----------|----------|--------------|----|

- *italic* Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.

- **bold** Highlights interface elements, such as menu names. Also used for emphasis in descriptive lists, where appropriate, and for ARM<sup>®</sup> processor signal names.

#### Feedback on this product

If you have any comments and suggestions about this product, contact your supplier and give:

• your name and company

- the serial number of the product

- details of the release you are using

- details of the platform you are using, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tools, including the version number and build numbers.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DUI 0498B

- if viewing online, the topic names to which your comments apply

- if viewing a PDF version of a document, the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

ARM periodically provides updates and corrections to its documentation on the ARM Information Center, together with knowledge articles and *Frequently Asked Questions* (FAQs).

#### Other information

- ARM Information Center, http://infocenter.arm.com/help/index.jsp

- ARM Technical Support Knowledge Articles, http://infocenter.arm.com/help/topic/com.arm.doc.faqs/index.html

- ARM Support and Maintenance, http://www.arm.com/support/services/support-maintenance.php.

## Chapter 2 Getting started with the debug hardware configuration utilities

The following topics describe how to get started with using the debug hardware configuration utilities:

- About the debug hardware configuration utilities on page 2-2

- Starting the debug hardware configuration utilities on page 2-3

- Scanning for available debug hardware units on page 2-5

- *Identifying a debug hardware unit* on page 2-7

- *Connecting to a debug hardware unit* on page 2-8.

## 2.1 About the debug hardware configuration utilities

The debug hardware configuration utilities enable you to connect to the debug hardware unit that provides the interface between your development platform and your PC. The following utilities are provided:

#### **RVI Config IP utility**

Used to configure the IP address on a debug hardware unit. This enables you to access the unit over Ethernet.

#### **RVConfig utility**

Used to configure a debug hardware unit. This enables you to:

- Identify the target devices on your development platform. These devices can be one or more processors, and optional trace devices or CoreSight<sup>™</sup> devices.

- Configure debug hardware and target-related features that are appropriate to correctly debug your development platform.

- Save the configuration to a device configuration file. The device configuration file is used by your debugger to connect to each target processor on your development platform.

#### **RVI Update utility**

Used to update the firmware and devices on a debug hardware unit and probe.

#### — Note ———

This document applies to the ARM<sup>®</sup> DSTREAM<sup>™</sup> debug and trace unit and the ARM RVI<sup>™</sup> debug unit. The term trace hardware refers to:

- the built-in trace hardware of a DSTREAM unit

- an ARM RVT or ARM RVT2<sup>™</sup> trace capture unit for RVI.

Differences in debug and trace hardware features between the units are explicitly stated.

#### 2.1.1 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- Scanning for available debug hardware units on page 2-5

- *Connecting to a debug hardware unit* on page 2-8

- Chapter 3 Configuring network settings for your debug hardware unit

- Chapter 4 Managing the firmware on your debug hardware unit

- Chapter 5 Creating debug hardware target configurations.

## 2.2 Starting the debug hardware configuration utilities

How you start the required debug hardware configuration utility depends on:

- your PC operating system

- whether you installed the host software with an ARM® software development product

- whether you are running a debugger session.

— Note —

For information about debugging with your own debugger, see your debugger documentation.

#### 2.2.1 Starting the RVConfig utility on Windows

To start the required debug hardware configuration utility on Windows platforms:

1. Select Start  $\rightarrow$  All Programs  $\rightarrow$  product\_group  $\rightarrow$  option\_path

where *product\_group* and *option\_path* are the names used by your ARM software development product.

- 2. Select the option for the utility you want to use:

- select *name* Config IP to start the RVI Config IP utility

- select *name* Configuration to start the RVConfig utility

- select *name* Update to start the RVI Update utility

where *name* is the name used by your ARM software development product.

\_\_\_\_\_ Note \_\_\_\_\_

Be aware that an option for the RVConfig utility might not be available on the **Start** menu for some ARM products.

For more information, see the documentation for your ARM software development product.

#### 2.2.2 Starting the RVConfig utility on Red Hat Linux

To start the required debug hardware configuration utility on Red Hat Linux platforms, select the appropriate shortcut. The shortcut depends on the version of Red Hat Linux and the desktop environment that you are using.

If no desktop shortcut is available, at the command-line:

1. Run the following setup script to configure the paths:

#### source RVDS41env.posh

- 2. Enter the command for the utility you want to use:

- enter **rviconfigip** to start the RVI Config IP utility

- enter **rvconfig** to start the RVConfig utility

- enter **rviupdate** to start the RVI Update utility.

#### 2.2.3 Accessing the RVConfig utility from your Debugger

You can access the RVConfig utility directly from your debugger. See your debugger documentation for details on how to do this.

### 2.2.4 See also

#### Tasks

- Scanning for available debug hardware units on page 2-5

- *Connecting to a debug hardware unit* on page 2-8.

## 2.3 Scanning for available debug hardware units

To scan for available debug hardware units:

- 1. Start the required configuration utility, for example RVConfig.

- 2. Click the **Scan** button to scan for debug hardware units that are connected to your local network or to a USB port on your PC. The **Scan** button becomes animated to indicate that a scan is in progress. When the configuration utility finds a unit, it adds it to the list of available units. The following figure shows an example:

| RVConfig<br>ile View Help |          |                                                                                     |                                                                          |                                                                                                       |                |

|---------------------------|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|

| No connection             | RealView | ICE browser                                                                         |                                                                          |                                                                                                       | Stopped        |

|                           | Access   | Host Name                                                                           | IP Address                                                               | Ethernet Address                                                                                      | Debug Hardware |

|                           |          | DStream<br>DStream02<br>rvi27<br>rvi29<br>rvi30<br>CP/IP Devices<br>ess / Host Name | 10.1.202.153<br>10.1.202.21<br>10.1.202.39<br>10.1.202.26<br>10.1.202.30 | 00:02:F7:00:38:5F<br>00:02:F7:00:06:FC<br>00:02:F7:00:0C:38<br>00:02:F7:00:1A:34<br>00:02:F7:00:20:B4 | RealView ICE   |

|                           |          | Co                                                                                  | nnect                                                                    | Identify                                                                                              |                |

|                           |          |                                                                                     |                                                                          |                                                                                                       |                |

|                           |          |                                                                                     |                                                                          |                                                                                                       |                |

|                           |          |                                                                                     |                                                                          |                                                                                                       |                |

Figure 2-1 RVConfig utility

—— Note ———

Any unit shown in light gray is one that has responded to browse requests but does not have a valid IP address. You cannot connect to that unit by TCP/IP until you have configured it for use on your network.

The scan tool searches for debug hardware units that are connected to your local network or USB ports on your PC. The units found are listed in the browser on the right of the window.

\_\_\_\_\_ Note \_\_\_\_\_

Units that are connected to different networks do not appear in the configuration utility. Consequently, if you want to connect to a debug hardware unit on a separate network, you must know the IP address of that unit.

If you want to stop scanning, click the **Scan** button. You can click the **Scan** button again at any time to force a rescan for available debug hardware units and update the list.

3. Select **Exit** from the **File**. This disconnects from any connected unit, and exits the configuration utility.

#### 2.3.1 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- *Identifying a debug hardware unit* on page 2-7

- *Connecting to a debug hardware unit* on page 2-8

- Chapter 3 Configuring network settings for your debug hardware unit.

## 2.4 Identifying a debug hardware unit

If you have multiple debug hardware units on a network, you can identify the unit you want to access from the configuration utility.

To identify the debug hardware unit you want to access:

- 1. Select a unit from the list, or enter an IP address of a unit if it is on a different network.

- 2. Click **Identify**.

The identification indicators on the selected debug hardware unit flash for 5 seconds. If you have selected the wrong unit, select another unit from the list and repeat this step.

\_\_\_\_\_ Note \_\_\_\_\_

On RVI, all LEDs on the front panel flash during identification.

On DSTREAM, the DSTREAM logo flashes during identification.

#### 2.4.1 See also

#### Tasks

- Scanning for available debug hardware units on page 2-5

- *Connecting to a debug hardware unit* on page 2-8

- Chapter 3 Configuring network settings for your debug hardware unit.

#### Reference

*ARM<sup>®</sup> DSTREAM<sup>™</sup> Setting Up the Hardware*:

• The DSTREAM debug and trace unit, .../com.arm.doc.dui0481b/CHDCJEFH.html.

$ARM^{\otimes} RVI^{m}$  and  $RVT^{m}$  Setting Up the Hardware:

• The RVI debug unit, ../com.arm.doc.dui0481b/CHDCJEFH.html.

### 2.5 Connecting to a debug hardware unit

You must connect to your debug hardware unit to create a configuration file that contains details of your target hardware and the debug hardware. The configuration file is required by your debugger to connect to your target development platform and debug your software.

#### 2.5.1 Prerequisites

Before you can connect to a debug hardware unit, make sure you have:

- 1. Set up, or have access to, the debug hardware unit that interfaces with your development platform.

- 2. Installed the correct version of the host software on your PC for your debug hardware unit.

#### 2.5.2 Procedure

To connect to a debug hardware unit:

- 1. Start the required configuration utility, for example the RVConfig utility.

- 2. If you do not see any debug hardware units listed for your local network, click the **Scan** button. The **Scan** button becomes animated to indicate that a scan is in progress. When the utility finds a debug hardware unit on your local network, it is added to the list of available units. The following figure shows an example:

| RVConfig        |          |                                                                                     |                                                                          |                                                                                                       |                                                                    |

|-----------------|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| File View Help  |          |                                                                                     |                                                                          |                                                                                                       |                                                                    |

| 🗅 🚅 🔲 🛄 🤗       |          |                                                                                     |                                                                          |                                                                                                       |                                                                    |

| I No connection | RealView | ICE browser                                                                         |                                                                          |                                                                                                       | Stopped                                                            |

|                 | Access   | Host Name                                                                           | IP Address                                                               | Ethernet Address                                                                                      | Debug Hardware                                                     |

|                 |          | DStream<br>DStream02<br>rvi27<br>rvi29<br>rvi30<br>CP/IP Devices<br>ess / Host Name | 10.1.202.153<br>10.1.202.21<br>10.1.202.39<br>10.1.202.26<br>10.1.202.30 | 00:02:F7:00:3B:5F<br>00:02:F7:00:06:FC<br>00:02:F7:00:00:32<br>00:02:F7:00:1A:34<br>00:02:F7:00:20:B4 | DSTREAM<br>DSTREAM<br>RealView ICE<br>RealView ICE<br>RealView ICE |

|                 |          | Co                                                                                  | nnect                                                                    | Identify                                                                                              |                                                                    |

|                 |          |                                                                                     |                                                                          |                                                                                                       |                                                                    |

|                 |          |                                                                                     |                                                                          |                                                                                                       |                                                                    |

|                 |          |                                                                                     |                                                                          |                                                                                                       | .::                                                                |

#### Figure 2-2 RVConfig utility showing debug hardware units

\_\_\_\_\_ Note \_\_\_\_\_

The scan tool only searches for debug hardware units that are connected to your local network or USB ports on your PC. Therefore, units that are connected to a different network do not appear in the configuration utility. Consequently, if you want to connect to a debug hardware unit that is not accessible on your local network, ensure that you know the IP address of that debug hardware unit.

Any unit shown in light gray is one that has responded to browse requests but does not have a valid IP address. You cannot connect to that unit by TCP/IP until you have configured it for use on your network.

Alternatively, connect the debug hardware unit directly to your PC using a USB cable.

- 3. If multiple units are listed, and you are unsure about the debug hardware unit you want to use:

- a. Select a unit in the list, or enter an IP address of a unit on a different network.

- b. Click **Identify**. The identification indicators on the unit flash for five seconds.

—— Note ———

On RVI, all LEDs on the front panel flash during identification. On DSTREAM, the DSTREAM logo flashes during identification.

- 4. To connect to your required unit, select the unit and click **Connect**. Alternatively, do one of the following:

- Double-click on the unit you want to connect to.

- In the IP Address/Host Name field, enter either the IP address or host name of the device you want to connect to and click **Connect**.

When a connection has been established, the configuration utility display changes to show the configuration features provided by that utility.

If you have problems connecting to a debug hardware unit, you must troubleshoot the debug hardware connections.

5. Select **Exit** from the **File** menu. This disconnects from any connected unit, and exits the configuration utility.

#### 2.5.3 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- Scanning for available debug hardware units on page 2-5

- Scanning for available debug hardware units on page 2-5

- Chapter 3 Configuring network settings for your debug hardware unit

- Chapter 10 Troubleshooting your debug hardware unit.

#### Reference

*ARM*<sup>®</sup> *DSTREAM*<sup>™</sup> *Setting Up the Hardware*:

The DSTREAM debug and trace unit, ../com.arm.doc.dui0481b/CHDCJEFH.html.

$ARM^{\mathbb{R}} RVI^{\mathbb{T}}$  and  $RVT^{\mathbb{T}}$  Setting Up the Hardware:

• The RVI debug unit, ../com.arm.doc.dui0481b/CHDCJEFH.html.

## Chapter 3 Configuring network settings for your debug hardware unit

The following topics describe how to configure the network settings for your debug hardware unit:

- *About configuring network settings* on page 3-2

- Determining the correct network settings on page 3-3

- The Configure debug\_hardware device dialog box on page 3-4

- The Configure new debug\_hardware device dialog box on page 3-6

- Debug hardware unit network settings on page 3-7

- Configuring the network settings for a debug hardware unit on page 3-8

- Modifying the network settings for a debug hardware unit on page 3-10

- *Restarting your debug hardware unit* on page 3-12

- *Troubleshooting* on page 3-13.

## 3.1 About configuring network settings

The configuration process depends on the way in which the debug hardware unit is connected to the host computer, and whether or not your network uses *Dynamic Host Configuration Protocol* (DHCP).

If you have connected your debug hardware unit to an Ethernet network or directly to the host computer using an Ethernet cross-over cable, you must configure the network settings before you can use the unit for debugging. You have only to configure the network settings once.

The following connections are possible:

- Your debug hardware unit is connected to your local network that uses DHCP. In this situation, you do not have to know the Ethernet address of the unit, but you must enable DHCP.

- Your debug hardware unit is connected to your local network that does not use DHCP. In this situation, you must assign a static IP address to the debug hardware unit.

— Note —

If you have connected your debug hardware unit directly to the host computer using a USB cable, and you do not intend to connect it to a network, you do not have to configure the network settings.

#### 3.1.1 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- Determining the correct network settings on page 3-3

- Configuring the network settings for a debug hardware unit on page 3-8

- Chapter 10 Troubleshooting your debug hardware unit.

*ARM<sup>®</sup> DSTREAM<sup>™</sup> Setting Up the Hardware*:

- Connecting the DSTREAM debug and trace unit, .../com.arm.doc.dui0481b/I1004916.html ARM<sup>®</sup> RVI<sup>™</sup> and RVT<sup>™</sup> Setting Up the Hardware:

- Connecting the RVI debug unit, ../com.arm.doc.dui0515b/I1004916.html

#### Reference

• Debug hardware unit network settings on page 3-7.

## 3.2 Determining the correct network settings

Before you can configure the network settings, you must first determine the correct network settings for your debug hardware unit. To do this, you must consult with the system administrator for your network.

The information that you require depends on whether your network uses *Dynamic Host Configuration Protocol* (DHCP):

#### Table 3-1 Required debug hardware network settings

| Information      | Using DHCP | Not using DHCP |

|------------------|------------|----------------|

| Host Name        | Yes        | Yes            |

| IP Address       | -          | Yes            |

| Default Gateway  | -          | Yes            |

| Subnet Mask      | -          | Yes            |

| Ethernet Address | Yes        | Yes            |

| Ethernet Type    | Yes        | Yes            |

#### 3.2.1 See also

#### Tasks

• Starting the debug hardware configuration utilities on page 2-3.

#### Reference

- The Configure debug\_hardware device dialog box on page 3-4

- *The Configure new debug\_hardware device dialog box* on page 3-6.

## 3.3 The Configure *debug\_hardware* device dialog box

The Configure *debug\_hardware* device dialog box enables you to modify the network settings on a debug hardware unit that has previously been configured. The following figure shows an example:

| 📽 Configure Rea  | alView ICE device ? 🔀 |

|------------------|-----------------------|

| Settings         |                       |

| DHCP             |                       |

| Host Name        |                       |

| IP Address       | 10.1.202.23           |

| Default Gateway  | 10.1.202.1            |

| Subnet Mask      | 255.255.255.0         |

| Ethernet Address | 00:02:F7:00:0E:3C     |

| Ethernet Type    | Auto-Detect 💌         |

| Configure        | Cancel Help           |

#### Figure 3-1 The Configure debug\_hardware device dialog box

-Note -

You can modify the settings only for a debug hardware unit that is on your local network or that is connected to a USB port on your PC.

The network settings available depend on whether or not your network uses *Dynamic Host Configuration Protocol* (DHCP):

- If your network uses DHCP, you must know:

- the hostname that you want to use for your unit (if any)

- the Ethernet type of your network.

- If your network does not use DHCP, you must know:

- the hostname that you want to use for your unit (if any)

- the IP address that you want to use for your unit

- the default gateway for your network (if it has one)

- the subnet mask for your network.

- the Ethernet type of your network.

— Note —

The Ethernet Address field is read-only.

After setting up the network settings, click Configure to write the values to the unit.

Click Exit to close the Configure debug\_hardware device dialog box

#### 3.3.1 See also

#### Tasks

- *About configuring network settings* on page 3-2

- Determining the correct network settings on page 3-3

- Configuring the network settings for a debug hardware unit on page 3-8

- Modifying the network settings for a debug hardware unit on page 3-10

- *Troubleshooting* on page 3-13.

#### Reference

- The Configure new debug\_hardware device dialog box on page 3-6

- *Debug hardware unit network settings* on page 3-7.

### 3.4 The Configure new *debug\_hardware* device dialog box

The Configure new *debug\_hardware* device dialog box enables you to:

- configure the network settings for a debug hardware unit that has not been previously configured

- configure the network settings for a debug hardware unit that is on a different subnet.

The following figure shows an example:

| 📲 Configure nev  | v RealView ICE device 🛛 🕐 |

|------------------|---------------------------|

| Settings         |                           |

| DHCP             |                           |

| Host Name        |                           |

| IP Address       | 0.0.0.0                   |

| Default Gateway  | 0.0.0.0                   |

| Subnet Mask      | 0.0.0.0                   |

| Ethernet Address | 00:00:00:00:00:00         |

| Ethernet Type    | Auto-Detect               |

| Identify         | Configure Help Exit       |

#### Figure 3-2 The Configure new debug\_hardware device dialog box

The network settings available depend on whether or not your network uses *Dynamic Host Configuration Protocol* (DHCP):

- If your network uses DHCP, you must know:

- the hostname that you want to use for your unit (if any)

- the Ethernet address of unit

- the Ethernet type of your network.

- If your network does not use DHCP, you must know:

- the hostname that you want to use for your unit (if any)

- the IP address that you want to use for your unit

- the default gateway for your network (if it has one)

- the subnet mask for your network.

- the Ethernet address of unit

- the Ethernet type of your network.

If more than one unit is listed in the browser, click **Identify** to identify your unit. The Identification LEDs on the selected unit flash for five seconds.

After setting up the network settings, click **Configure** to write the values to the unit.

Click Exit to close the Configure new debug\_hardware device dialog box

#### 3.4.1 See also

#### Tasks

- About configuring network settings on page 3-2

- Determining the correct network settings on page 3-3

- Configuring the network settings for a debug hardware unit on page 3-8.

#### Reference

*Debug hardware unit network settings* on page 3-7.

## 3.5 Debug hardware unit network settings

The following network settings are available for a debug hardware unit:

- **DHCP** Enables or disables *Dynamic Host Configuration Protocol* (DHCP):

- If your network uses DHCP, you must know the hostname that you want to use for your debug hardware unit (if any).

— Note —

You do not have to know the IP address for your debug hardware unit, or the default gateway and subnet mask for your network, because these settings are fetched from a DHCP server on your network.

- If your network does not use DHCP, you must know:

- the hostname to use for your debug hardware unit (if any)

- the IP address to use for your debug hardware unit

- the default gateway for your network (if it has one)

- the subnet mask for your network.

- **Host Name** The host name for the unit. This must contain only the alphanumeric characters (A to Z, a to z, and 0 to 9) and the character, and must be no more than 39 characters long.

IP Address The static IP address to use when DHCP is disabled.

#### **Default Gateway**

The default gateway to use when DHCP is disabled.

#### Subnet Mask

The subnet mask to use when DHCP is disabled.

#### **Ethernet Address**

The Ethernet address of the unit.

#### Ethernet Type

The type of network you are using:

- If you know the type of network, select the type. The options are:

- 10-MBit, Half Duplex

- 10-MBit, Full Duplex

- 100-MBit, Half Duplex

- 100-MBit, Full Duplex.

- Otherwise, select Auto-Detect.

#### 3.5.1 See also

#### Tasks

- About configuring network settings on page 3-2

- Configuring the network settings for a debug hardware unit on page 3-8

- *Troubleshooting* on page 3-13.

#### Reference

- The Configure debug\_hardware device dialog box on page 3-4

- *The Configure new debug\_hardware device dialog box* on page 3-6.

## 3.6 Configuring the network settings for a debug hardware unit

If you have a debug hardware unit that does not have a valid IP address, or is on a different network, you must manually enter the Ethernet address during configuration.

#### 3.6.1 Prerequisites

Before you can configure the network settings, you must first determine the correct network settings for your debug hardware unit:

- If you do not want to use DHCP, then you must obtain an IP Address, Default Gateway, and Subnet Mask from your network administrator.

- If you want to use DHCP, you must inform your network administrator of the Ethernet Address of the unit, so that it can be added to the DHCP server.

#### 3.6.2 Procedure

To configure your new debug hardware unit:

- 1. Open the RVI Config IP utility.

- 2. If the debug hardware unit is on your local network or connected to a USB port on your PC, continue at step 3.

Otherwise, continue at step 6.

**3**. Click the **Scan** tool to scan for debug hardware units.

#### \_\_\_\_\_ Note \_\_\_\_\_

Only debug hardware units that are on your local network or connected to a USB port on your PC are listed.

- 4. Select the debug hardware unit you want to configure.

- 5. Click the **Identify** tool to verify that the identification LEDs flash on the correct debug hardware unit.

- 6. Click the **Config New** tool. The Configure new *debug\_hardware* device dialog box appears, as shown in the following figure:

| 🏁 Configure new RealView ICE device 🛛 🔹 💽 |                   |   |  |  |  |  |

|-------------------------------------------|-------------------|---|--|--|--|--|

| Settings                                  |                   |   |  |  |  |  |

| DHCP                                      |                   |   |  |  |  |  |

| Host Name                                 |                   |   |  |  |  |  |

| IP Address                                | 0.0.0.0           |   |  |  |  |  |

| Default Gateway                           | 0.0.0.0           |   |  |  |  |  |

| Subnet Mask                               | 0.0.0.0           |   |  |  |  |  |

| Ethernet Address                          | 00:00:00:00:00:00 |   |  |  |  |  |

| Ethernet Type                             | Auto-Detect       | • |  |  |  |  |

| Identify Configure Help Exit              |                   |   |  |  |  |  |

#### Figure 3-3 The Configure new debug\_hardware device dialog box

- 7. Determine the Ethernet address of your debug hardware unit by reading the label on the side of the unit, and enter it into the Ethernet Address field.

- 8. If you are not using DHCP:

- a. Deselect **DHCP**.

- b. Enter the required details in the following fields:

- IP Address

- Default Gateway

- Subnet Mask.

- c. Continue at step 9.

- 9. If you are using DHCP, select **DHCP**.

- 10. Enter the hostname in the Host Name field. This must contain only the alphanumeric characters (A-Z, a-z, and 0-9) and the character, and must be no more than 255 characters long.

- 11. Select the required Ethernet Type:

- if you know the type of network that you are using, select that type

- otherwise, select Auto-Detect.

#### 12. Click Configure.

The debug hardware unit restarts. During the restart the unit is removed from the list of units. When the restart is complete, the unit re-appears in the list of units, with the new network settings.

\_\_\_\_\_Note \_\_\_\_\_

If the debug hardware unit is using DHCP, the list of units might display its **IP Address** as 127.0.0.2. This is a dummy address that the debug hardware unit uses when it fails to obtain an IP address from the DHCP server.

The list of units shows the correct address if the DHCP server has assigned it.

#### 3.6.3 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- Scanning for available debug hardware units on page 2-5

- Determining the correct network settings on page 3-3

- *Troubleshooting* on page 3-13

- Chapter 10 Troubleshooting your debug hardware unit.

#### Concepts

• About configuring network settings on page 3-2.

## 3.7 Modifying the network settings for a debug hardware unit

You can modify the network settings of a debug hardware unit only if that unit is on your local network or connected to a USB port on your PC.

— Note –

If the debug hardware unit is on a different network, you must use the Configure New *debug\_hardware* device dialog box.

#### 3.7.1 Prerequisites

Before you can configure the network settings, you must first determine the correct network settings for your debug hardware unit:

- If you do not want to use DHCP, then you must obtain an IP Address, Default Gateway, and Subnet Mask from your network administrator.

- If you want to use DHCP, you must inform your network administrator of the Ethernet Address of the unit, so that it can be added to the DHCP server.

### 3.7.2 Procedure

To configure your debug hardware unit by manually entering an Ethernet address:

- 1. Open the RVI Config IP utility.

- 2. Click the **Scan** tool to scan for debug hardware units.

3. Select the debug hardware unit you want to modify.

- 4. Click the **Identify** tool to verify that the identification LEDs flash on the correct debug hardware unit.

- 5. Click the **Configure** tool to display the Configure *debug\_hardware* device dialog box. An example is shown in the following figure:

#### Figure 3-4 The Configure debug\_hardware device dialog box

The Ethernet Address field is read-only.

6. If you are not using DHCP:

Note -

- a. Deselect **DHCP**.

- b. Enter the required details in the following fields:

- IP Address

- Default Gateway

- Subnet Mask.

- c. Continue at step 9.

- 7. If you are using DHCP, select **DHCP**.

- 8. Enter the hostname in the Host Name field. This must contain only the alphanumeric characters (A-Z, a-z, and 0-9) and the character, and must be no more than 255 characters long.

- 9. Select the required Ethernet Type:

- if you know the type of network that you are using, select that type

- otherwise, select **Auto-Detect**.

#### 10. Click Configure.

The debug hardware unit restarts. During the restart, the unit is not present in the list. When the unit has restarted, it re-appears in the list of units with the new network settings.

#### — Note —

If the debug hardware unit is using DHCP, the list of units might display its **IP Address** as 127.0.0.2. This is a dummy address that the debug hardware unit uses when it fails to obtain an IP address from the DHCP server.

The list of units shows the correct address if the DHCP server has assigned it.

#### 3.7.3 See also

#### Tasks

- Starting the debug hardware configuration utilities on page 2-3

- Scanning for available debug hardware units on page 2-5

- Determining the correct network settings on page 3-3

- *Troubleshooting* on page 3-13

- Configuring the network settings for a debug hardware unit on page 3-8

- Chapter 10 Troubleshooting your debug hardware unit.

#### Concepts

• *About configuring network settings* on page 3-2.

#### Reference

- The Configure debug\_hardware device dialog box on page 3-4

- *The Configure new debug\_hardware device dialog box* on page 3-6.

## 3.8 Restarting your debug hardware unit

The RVI Config IP utility restarts the networking software on the debug hardware unit whenever you change its settings. If necessary, select **Restart** from the **RVI** menu to force the networking software to restart.

You might want to restart the networking software on the debug hardware unit to get new network settings from the DHCP server. To do this, select **Restart** from the RVI menu.

#### 3.8.1 See also

#### Tasks

•

Starting the debug hardware configuration utilities on page 2-3.

## 3.9 Troubleshooting

If you encounter problems when configuring network settings for your debug hardware unit, see the following:

#### 3.9.1 Why can't I see my DSTREAM or RVI unit on the network?

Seeing or browsing for DSTREAM or RVI units on the network relies on the local area network (LAN) allowing propagation of broadcast packets (UDP) on ports 30000 and 30001. It is common to limit the propagation of these types of packets to a localized network region to prevent congestion, but it might be possible to allow propagation of packets on these specific ports. Contact your network administrator to request this modification.

— Note — —

This issue is seen when a DSTREAM or RVI unit is behind any network component that filters network traffic, such as a firewall.

#### 3.9.2 When is it appropriate to assign a fixed IP address to my DSTREAM or RVI unit?

If it is not possible to browse for the DSTREAM or RVI unit on the network using the tools, you can attempt to locate the unit by specifying the host name of the unit, for example MyDSTREAM.local.example.com.

If the host name cannot be resolved, you can use an IP address, for example 192.168.1.16. In this case, you might want to assign a fixed IP address to the DSTREAM or RVI unit to prevent this IP address from changing. To request a fixed IP address, contact your network administrator. When the address is assigned to the DSTREAM or RVI unit, you can confirm its correct operation by using the ping command from a DOS or UNIX prompt prior to connecting the tools.

A fixed IP address is also appropriate when an Ethernet cross-over cable is used. In this case, a private network between the host PC and the unit is created, although this might not be necessary due to the availability of a USB connection.

#### 3.9.3 Why does my debug connection fail when I connect the Mictor cable to my target?

Some target systems have their debug signals connected to both a Mictor trace connector and a separate debug-only connector. In this scenario, if you connect the Mictor cable alongside another debug cable, there is effectively a large unterminated stub on the debug signals. This can cause the debug interface to become unstable. To solve this problem, configure the DSTREAM or RVI software to use the Mictor cable for both the debug and trace signals, and disconnect any other debug cables.

#### 3.9.4 See also

#### Tasks

- Configuring the network settings for a debug hardware unit on page 3-8

- Modifying the network settings for a debug hardware unit on page 3-10.

#### Concepts

- *The Configure debug\_hardware device dialog box* on page 3-4

- Debug hardware unit network settings on page 3-7.

## Chapter 4 Managing the firmware on your debug hardware unit

The following topics describe how to manage and update the software that is installed on the debug hardware unit, using the RVI Update utility:

- *About templates* on page 4-2

- *Viewing software version numbers* on page 4-3

- Installing a firmware update or patch on page 4-4

- *Upgrading an LVDS probe* on page 4-7

- *Restarting the debug hardware unit in RVI Update* on page 4-8.

## 4.1 About templates

The debug hardware unit stores templates for each supported device. These templates each define how to communicate with the device, and the settings that you can configure for that device.

#### 4.1.1 See also

## Tasks

•

- Viewing software version numbers on page 4-3

- *Installing a firmware update or patch* on page 4-4.

## 4.2 Viewing software version numbers

To view software version numbers, select **Version Info...** from the **RVI** menu in the RVI Update utility. The Version Info dialog box displays a window giving version information. An example is shown in the following figure:

| A Version Info                                                                                                                                                                                                                                                                                                                                                                                                                                        | ? 🗙               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| This is release version number 3.4.0<br>Build Number 18<br>JTAG Template for the ARM1020E core V1.<br>JTAG Template for the ARM1156T2-S core<br>JTAG Template for the ARM740T core V1.0<br>JTAG Template for the ARM1701D core V1.0<br>JTAG Template for the ARM1701D core V1.0<br>JTAG Template for the ARM1176J2F-S core<br>JTAG Template for the ARM1020E core V<br>JTAG Template for the ARM1020E core V<br>JTAG Template for the ARM1020E core V | OK<br>Help<br>Log |

#### Figure 4-1 Version information

The text above the scrolling list shows the version number of the software release that is installed, in the format:

This is release version number major.minor.patch

where:

| major | is the major | release | version | number |

|-------|--------------|---------|---------|--------|

| major | is the major | release | version | number |

*minor* is the minor release version number

*patch* is the patch level of the *major.minor* version.

The scrolling list shows the version number of each component of the installed software.

The Log... button enables you to save the version information to a file. To do this:

- 1. Click Log. The Select Log File Name dialog box is displayed.

- 2. Choose the location of the log file.

- 3. Click **Save** to save the log file.

- 4. Click **OK** to close the Version Info dialog box.

### 4.2.1 See also

#### Tasks

Installing a firmware update or patch on page 4-4.

## 4.3 Installing a firmware update or patch

ARM periodically releases updates and patches to the firmware that is installed on a debug hardware unit. Each update or patch is released as a component file with the suffix .rvi for RVI, and suffix .dstream for DSTREAM. These might extend the capabilities of your debug hardware, or might fix an issue that has become apparent. You can obtain these files from the ARM web site.

If you want to restore the firmware to its original state after installing an upgrade, you can reinstall the original component file, obtainable from the ARM website. See the *Getting Started* document for your ARM product for more information.

To install an update or patch to the firmware on a debug hardware unit:

In the RVI Update utility, click the **Install Firmware** tool. The Select Firmware Update to Install dialog box is displayed. An example is shown in the following figure:

| Select Firmwar         | e Update to Ins | tall                     |   |           | ? 🗙    |

|------------------------|-----------------|--------------------------|---|-----------|--------|

| Look in:               | 🚞 Firmware      |                          | • | + 🗈 📸 📰 - |        |

| My Recent<br>Documents | <b>i</b> 3.4    |                          |   |           |        |

| My Documents           |                 |                          |   |           |        |

| My Computer            |                 |                          |   |           |        |

| Sector 1               |                 |                          |   |           |        |

| My Network<br>Places   | File name:      |                          |   | -         | Open   |

|                        | Files of type:  | RVI Update files (*.rvi) |   | •         | Cancel |

Figure 4-2 Selecting the component file to install

- 2. Navigate to the directory containing the component file for the update or patch that you want to install, and select the required file.

- 3. Click **Open**. After a short delay, a dialog box appears that describes what is in the component file, as shown in the following figure:

#### Figure 4-3 Confirming that you want to install the component file

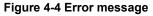

When attempting to install an update file, if you are using an older version of RVI Update, for example a pre-RVI v1.5 release, an error message appears as shown in the following figure:

| A RVI Update - rvihost33 |                                                                                                  |

|--------------------------|--------------------------------------------------------------------------------------------------|

| File View RVI Help       |                                                                                                  |

| RealView ICE             | Description           Version           Version           0.0.0           Comments           N/A |

|                          |                                                                                                  |

Before proceeding with your intended installation, you must upgrade your RVI Update utility to the latest software.

-Note —

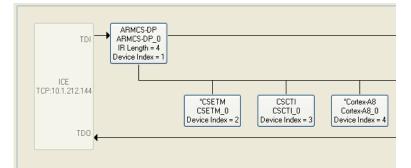

Similarly, if you are using a version of hardware that is incompatible with the firmware you are attempting to install, an error message similar to the one shown in the following figure:

| 💐 RVI | Update 🛛 🗙                                                                                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ⊗     | The update file you are using is not compatible with this version of RealView ICE.<br>Please apply a later firmware update.<br>The RealView ICE will now reboot. |

|       | OK                                                                                                                                                               |

Figure 4-5 Error when using an incompatible version of hardware

4. In the Install update dialog box, click **Continue** to confirm that you want to install the components, or **Cancel** to make no change to the debug hardware unit. The RVI Update utility then uploads the component file to the debug hardware unit. The debug hardware unit unpacks the component file, and installs the update or patch that it contains. The progress of the installation is displayed as shown in the following figure:

| RVI Update                     |     |

|--------------------------------|-----|

| Installing update. Please wait |     |

|                                | 54% |

| Abort                          |     |

#### Figure 4-6 Progress during an installation

The debug hardware unit might automatically reboot itself as part of this procedure, depending on the patch or update that you are installing. The progress of the reboot is displayed as shown in the following figure:

| RVI Update                             |

|----------------------------------------|

| RealView ICE is rebooting. Please wait |

| 75%                                    |

| Abort                                  |

#### Figure 4-7 Progress when rebooting during an installation

During the installation process, the FLASH LED lights up, showing that the unit is accessing its internal flash storage. During this time, do not disconnect power from the debug hardware unit. If a problem occurs during the installation, you must troubleshoot the firmware upgrade installation.

— Note —

While an installation is taking place, the **Abort** button is enabled. This means that you can safely stop the installation from proceeding by clicking this button. If the **Abort** button is not enabled, for example during rebooting, you cannot stop the reboot.

When the installation is complete, a message is displayed as shown in the following figure:

| 🚑 RVI | Update 🛛 🗙                                                                                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ٩     | The update has been successfully installed onto the RealView ICE.<br>Please close this application before attempting to use the RealView ICE Configuration tool. |

|       | ОК                                                                                                                                                               |

#### Figure 4-8 Message showing a successful installation

#### 4.3.1 See also

#### Tasks

• *Upgrading an LVDS probe* on page 4-7.

#### Concepts

*Troubleshooting firmware upgrade installations* on page 10-9.

#### **Other information**

ARM web site, http://www.arm.com

# 4.4 Upgrading an LVDS probe

You can use the RVI Update utility to install an upgrade to your *Low Voltage Differential Signaling* (LVDS) probe. This upgrade procedure is necessary only if you want to make use of the *Serial Wire Debug* (SWD) feature. This is a once-only upgrade that is required if your LVDS probe was released with RVI v3.0, because this type of probe is not SWD-capable.

To upgrade your LVDS probe:

- 1. In the RVI Update utility, select Upgrade LVDS Probe... from the RVI menu.

- 2. You are prompted to confirm your option to upgrade the probe. Select **Yes**, and the RVI Update utility begins the update process, during which you are reminded not to disconnect the probe, nor to power off your debug hardware unit, until the process is completed. This is shown in the following figure:

| RVI Update                                                           |

|----------------------------------------------------------------------|

| Upgrading probe<br>Do not disconnect probe or power off RealView ICE |

|                                                                      |

Figure 4-9 Progress during probe update

#### — Note —

To perform the upgrade you must have v3.1 firmware or later installed on your debug hardware unit.

You must also have an LVDS probe that is at least at v2.

If you have a v1 probe (board number HPI-0090x), you must replace it with a later version. If so, contact ARM for more information.

#### 4.4.1 See also

# Tasks

*Installing a firmware update or patch* on page 4-4.

#### Concepts

*Troubleshooting firmware upgrade installations* on page 10-9.

### Reference

*ARM*<sup>®</sup> *DSTREAM*<sup>™</sup> *System and Interface Design Reference*:

Serial Wire Debug , ../com.arm.doc.dui0499b/BEHIADEG.html

$ARM^{\otimes} RVI^{m}$  and  $RVT^{m}$  System and Interface Design Reference:

Serial Wire Debug, ../com.arm.doc.dui0517b/yCHDBDBHI.html

# 4.5 Restarting the debug hardware unit in RVI Update

To restart the debug hardware unit, select **Restart** from the **RVI** menu. RVI Update reboots the debug hardware unit, waits for the reboot to finish, then reconnects automatically. A message is displayed telling you that debug hardware is rebooting.

# 4.5.1 See also

# Tasks

- Starting the debug hardware configuration utilities on page 2-3

- *Connecting to a debug hardware unit* on page 2-8

- Installing a firmware update or patch on page 4-4

- *Upgrading an LVDS probe* on page 4-7.

### Concepts

- Chapter 10 Troubleshooting your debug hardware unit

- *Viewing software version numbers* on page 4-3.

### Reference

• Chapter 3 Configuring network settings for your debug hardware unit.

# Chapter 5 Creating debug hardware target configurations

The following topics describe how to create a debug hardware configuration file with the RVConfig utility for use by your debugger:

- About creating debug hardware target configurations on page 5-3

- Creating a debug hardware configuration file on page 5-4

- Opening an existing debug hardware configuration file in RVConfig on page 5-6

- *Configuring a JTAG scan chain* on page 5-7

- *About configuring a device list* on page 5-9

- *Autoconfiguring a scan chain* on page 5-11

- *Adding devices to the scan chain* on page 5-12

- *Removing devices from the scan chain* on page 5-16

- Changing the order of devices on the scan chain on page 5-17

- Select Platform dialog box on page 5-18

- *Export As Platform dialog box* on page 5-19

- *Exporting a configuration to a platform file* on page 5-20

- Device Properties dialog box on page 5-21

- Setting the clock speed on page 5-24

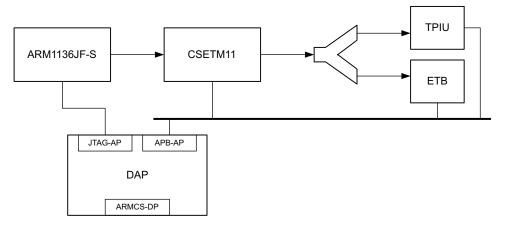

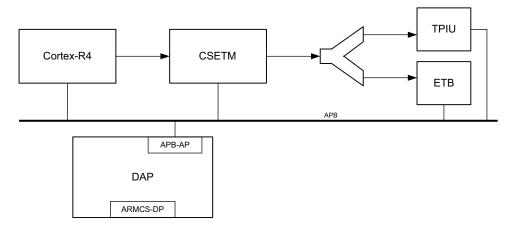

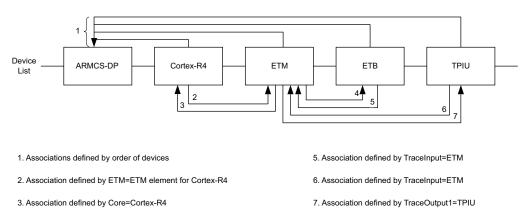

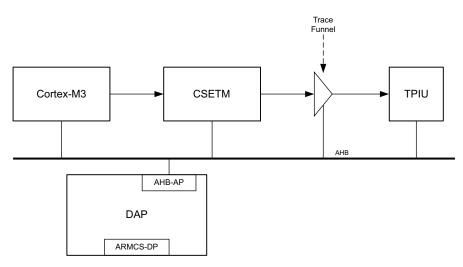

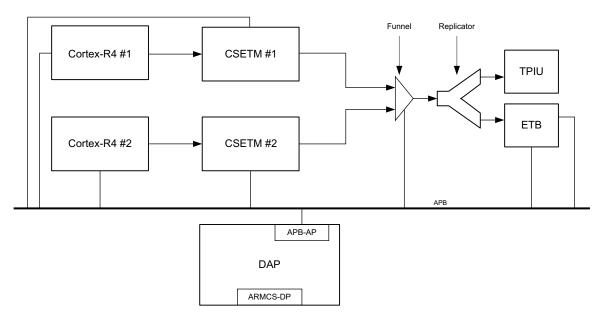

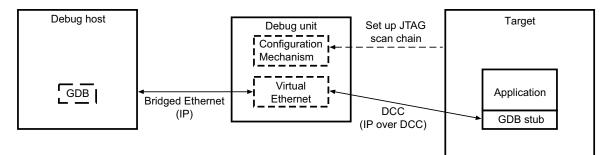

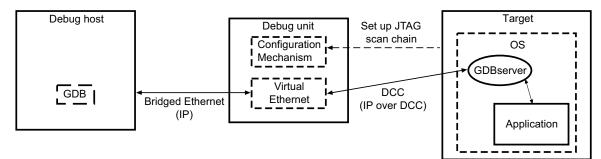

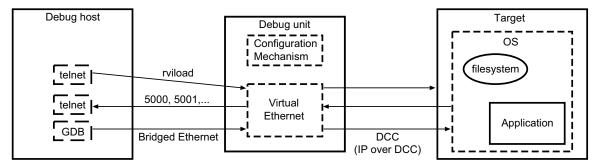

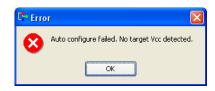

- *About adaptive clocking* on page 5-25